Ziyad Hakura Phones & Addresses

-

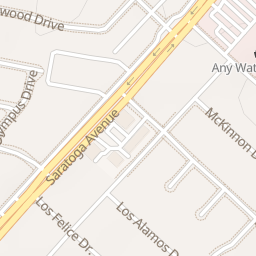

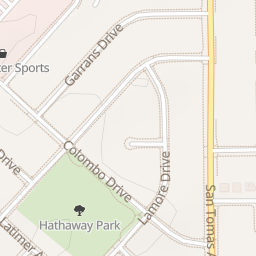

San Jose, CA

-

3875 Park Ave, Palo Alto, CA 94306 (650) 843-0612

-

Stanford, CA

-

704 Tennyson Dr, Gilroy, CA 95020 (408) 847-6408

-

2400 El Camino Real, Mountain View, CA 94040 (650) 625-1810

-

896 Middle Ave, Menlo Park, CA 94025 (650) 289-0620 (650) 323-7931

-

Redmond, WA

Publications

Us Patents

System And Method For Accelerating A Special Purpose Processor

View pageUS Patent:

7053901, May 30, 2006

Filed:

Dec 11, 2003

Appl. No.:

10/732445

Inventors:

Michael Brian Cox - Menlo Park CA, US

Ziyad S. Hakura - Palo Alto CA, US

John S. Montrym - Cupertino CA, US

Brad W. Simeral - San Francisco CA, US

Brian Keith Langendorf - Benicia CA, US

Blanton Scott Kephart - Dallas TX, US

Franck R. Diard - Mountain View CA, US

Ziyad S. Hakura - Palo Alto CA, US

John S. Montrym - Cupertino CA, US

Brad W. Simeral - San Francisco CA, US

Brian Keith Langendorf - Benicia CA, US

Blanton Scott Kephart - Dallas TX, US

Franck R. Diard - Mountain View CA, US

Assignee:

NVIDIA Corporation - Santa Clara CA

International Classification:

G06T 1/00

US Classification:

345503, 345506

Abstract:

Embodiments of the invention accelerate at least one special purpose processor, such as a GPU, or a driver managing a special purpose processor, by using at least one co-processor. Advantageously, embodiments of the invention are fault-tolerant in that the at least one GPU or other special purpose processor is able to execute all computations, although perhaps at a lower level of performance, if the at least one co-processor is rendered inoperable. The co-processor may also be used selectively, based on performance considerations.

System, Apparatus And Method For Predicting Accesses To A Memory

View pageUS Patent:

7206902, Apr 17, 2007

Filed:

Aug 17, 2004

Appl. No.:

10/921026

Inventors:

Ziyad S. Hakura - Mountain View CA, US

Brian Keith Langendorf - Benicia CA, US

Stefano A. Pescador - Sunnyvale CA, US

Radoslav Danilak - Santa Clara CA, US

Brad W. Simeral - San Francisco CA, US

Brian Keith Langendorf - Benicia CA, US

Stefano A. Pescador - Sunnyvale CA, US

Radoslav Danilak - Santa Clara CA, US

Brad W. Simeral - San Francisco CA, US

Assignee:

NVIDIA Corporation - Santa Clara CA

International Classification:

G06F 12/00

US Classification:

711137, 711118, 711154, 712207, 712237

Abstract:

A system, apparatus, and method are disclosed for predicting accesses to memory. In one embodiment, an exemplary apparatus comprises a processor configured to execute program instructions and process program data, a memory including the program instructions and the program data, and a memory processor. The memory processor can include a speculator configured to receive an address containing the program instructions or the program data. Such a speculator can comprise a sequential predictor for generating a configurable number of sequential addresses. The speculator can also include a nonsequential predictor configured to associate a subset of addresses to the address and to predict a group of addresses based on at least one address of the subset, wherein at least one address of the subset is unpatternable to the address.

Method And Apparatus To Accelerate Rendering Of Shadow Effects For Computer-Generated Images

View pageUS Patent:

7248261, Jul 24, 2007

Filed:

Dec 15, 2003

Appl. No.:

10/736953

Inventors:

Ziyad S. Hakura - Palo Alto CA, US

Assignee:

NVIDIA Corporation - Santa Clara CA

International Classification:

G06T 15/60

US Classification:

345426

Abstract:

The present invention provides for accelerating the generation of graphical images that include shadow effects by, for example, reducing the amount of data transmitted and/or stored necessary to render graphics based on stencil shadow volumes. In one embodiment, an exemplary apparatus is configured to render shadows using stencil shadow volumes. The apparatus includes a memory to store a degree of shadowing for each sample. A co-processor, which is coupled to the memory, is configured to generate an indicator that represents a common degree of shadowing associated with the subset of samples. In some cases, the apparatus includes a graphics processing unit (“GPU”), which is coupled to the co-processor, that is configured to render one or more shadows for a computer-generated image based on the indicator.

System, Apparatus And Method For Performing Look-Ahead Lookup On Predictive Information In A Cache Memory

View pageUS Patent:

7260686, Aug 21, 2007

Filed:

Aug 17, 2004

Appl. No.:

10/920995

Inventors:

Ziyad S. Hakura - Mountain View CA, US

Radoslav Danilak - Santa Clara CA, US

Brad W. Simeral - San Francisco CA, US

Brian Keith Langendorf - Benicia CA, US

Stefano A. Pescador - Sunnyvale CA, US

Dmitry Vyshetsky - Cupertino CA, US

Radoslav Danilak - Santa Clara CA, US

Brad W. Simeral - San Francisco CA, US

Brian Keith Langendorf - Benicia CA, US

Stefano A. Pescador - Sunnyvale CA, US

Dmitry Vyshetsky - Cupertino CA, US

Assignee:

Nvidia Corporation - Santa Clara CA

International Classification:

G06F 12/00

US Classification:

711137

Abstract:

A system, apparatus, and method are disclosed for storing predictions as well as examining and using one or more caches for anticipating accesses to a memory. In one embodiment, an exemplary apparatus is a prefetcher for managing predictive accesses with a memory. The prefetcher can include a speculator to generate a range of predictions, and multiple caches. For example, the prefetcher can include a first cache and a second cache to store predictions. An entry of the first cache is addressable by a first representation of an address from the range of predictions, whereas an entry of the second cache is addressable by a second representation of the address. The first and the second representations are compared in parallel against the stored predictions of either the first cache and the second cache, or both.

Screen Compression

View pageUS Patent:

7342590, Mar 11, 2008

Filed:

May 9, 2003

Appl. No.:

10/435073

Inventors:

John M. Danskin - Cranston RI, US

Ziyad S. Hakura - Palo Alto CA, US

Edward L. Riegelsberger - Fremont CA, US

Jason M. Musicer - San Jose CA, US

Stephen D. Lew - Sunnyvale CA, US

Ziyad S. Hakura - Palo Alto CA, US

Edward L. Riegelsberger - Fremont CA, US

Jason M. Musicer - San Jose CA, US

Stephen D. Lew - Sunnyvale CA, US

Assignee:

Nvidia Corporation - Santa Clara CA

International Classification:

G06T 9/00

G06K 9/36

G06K 9/36

US Classification:

345555, 382232

Abstract:

Methods, circuits, and apparatus for reducing memory bandwidth used by a graphics processor. Uncompressed tiles are read from a display buffer portion of a graphics memory and received by an encoder. The uncompressed tiles are compressed and written back to the graphics memory. When a tile is needed again before it has been modified, the compressed version is read from memory, uncompressed, and displayed. To reduce the number of unnecessary writes of compressed tiles to memory, a tile is only written to memory if it has remained static for some number of refresh cycles. Also, to prevent a large number of compressed tiles being written to the display buffer in one refresh cycle, the encoder can be throttled after a number of tiles have been written. Validity information can be stored for use by a CRTC. If a tile is updated, the validity information is updated such that invalid compressed data is not read from memory and displayed.

Method And Apparatus To Accelerate Rendering Of Shadows

View pageUS Patent:

7369126, May 6, 2008

Filed:

Nov 17, 2006

Appl. No.:

11/561322

Inventors:

Ziyad S. Hakura - Palo Alto CA, US

Assignee:

Nvidia Corporation - Santa Clara CA

International Classification:

G06T 15/60

US Classification:

345426

Abstract:

The present invention provides for accelerating the generation of graphical images that include shadow effects by, for example, reducing the amount of data transmitted and/or stored necessary to render graphics based on stencil shadow volumes. In one embodiment, an exemplary apparatus is configured to render shadows using stencil shadow volumes. The apparatus includes a memory to store a degree of shadowing for each sample. A co-processor, which is coupled to the memory, is configured to generate an indicator that represents a common degree of shadowing associated with the subset of samples. In some cases, the apparatus includes a graphics processing unit (“GPU”), which is coupled to the co-processor, that is configured to render one or more shadows for a computer-generated image based on the indicator.

System, Apparatus And Method For Issuing Predictions From An Inventory To Access A Memory

View pageUS Patent:

7441087, Oct 21, 2008

Filed:

Aug 17, 2004

Appl. No.:

10/920610

Inventors:

Ziyad S. Hakura - Mountain View CA, US

Brian Keith Langendorf - Benicia CA, US

Stefano A. Pescador - Sunnyvale CA, US

Radoslay Danilak - Santa Clara CA, US

Brad W. Simeral - San Francisco CA, US

Brian Keith Langendorf - Benicia CA, US

Stefano A. Pescador - Sunnyvale CA, US

Radoslay Danilak - Santa Clara CA, US

Brad W. Simeral - San Francisco CA, US

Assignee:

NVIDIA Corporation - Santa Clara CA

International Classification:

G06F 9/26

G06F 12/00

G06F 12/00

US Classification:

711137, 710244

Abstract:

A system, apparatus, and method are disclosed for managing predictive accesses to memory. In one embodiment, an exemplary apparatus is configured as a prediction inventory that stores predictions in a number of queues. Each queue is configured to maintain predictions until a subset of the predictions is either issued to access a memory or filtered out as redundant. In another embodiment, an exemplary prefetcher predicts accesses to a memory. The prefetcher comprises a speculator for generating a number of predictions and a prediction inventory, which includes queues each configured to maintain a group of items. The group of items typically includes a triggering address that corresponds to the group. Each item of the group is of one type of prediction. Also, the prefetcher includes an inventory filter configured to compare the number of predictions against one of the queues having the either the same or different prediction type as the number of predictions.

Apparatus, System, And Method For Z-Culling

View pageUS Patent:

7450120, Nov 11, 2008

Filed:

Dec 19, 2003

Appl. No.:

10/741115

Inventors:

Ziyad S. Hakura - Mountain View CA, US

Michael Brian Cox - Menlo Park CA, US

Brian K. Langendorf - Benicia CA, US

Brad W. Simeral - San Francisco CA, US

Michael Brian Cox - Menlo Park CA, US

Brian K. Langendorf - Benicia CA, US

Brad W. Simeral - San Francisco CA, US

Assignee:

Nvidia Corporation - Santa Clara CA

International Classification:

G06T 15/40

G06F 15/16

G06T 1/20

G06F 15/16

G06T 1/20

US Classification:

345421, 345422, 345503, 345506

Abstract:

A processor generates Z-cull information for tiles and groups of tiles. In one embodiment the processor includes an on-chip cache to coalesce Z information for tiles to identify occluded tiles. In a coprocessor embodiment, the processor provides Z-culling information to a graphics processor.